Recent Advancement in the Field of Analogue Layout Synthesis

Main Article Content

Abstract

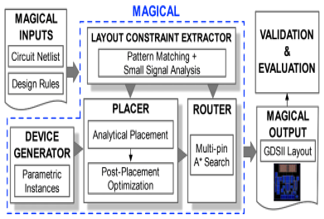

To diminish layout configuration time, simple layout creators favor alluding to inheritance plans and layouts instead of beginning without any preparation, or completely applying arrangement and directing apparatuses on the grounds that heritage layouts contain essentially plan skill. Subsequently, this paper presents the principal information based layout synthesis technique to produce new layouts by coordinating existent plan aptitude contained in the quality-supported heritage layouts however much as could reasonably be expected. Exploratory outcomes show that the proposed system with information mining can accomplish high layout reusage rate and thus the planners' layout inclination can be effectively held. Hierarchicalanalog layout generators go on from leaf cells ("locals") to sensibly greater blocks that are set and directed. The idea of unrefined cell layout is fundamental for plan execution. The framework recommended in this paper upgrades and arranges locals' presentation estimations during leaf cell layout. Consolidating layout parasitics and layout-subordinate impacts, it furnishes the spot and course engine with an assortment of better layout determinations as well as wire estimating rules for affiliations beyond the telephone. Our technique outflanks the opposition for FinFET-based plans of a high-repeat intensifier, a StrongARM comparator, and a completely differential VCO and is compelling with time-escalated manual layout.